教程或软件可以点“立即下载",具体也可以在"扫码支付"后联系QQ:2767376626或其它联系方式发对应下载地址.

◆ANSYS Electronics 2021信号SI与电源完整性PI仿真分析视频教程-6344分钟(超长时间)

◆01.HFSS 信号完整性仿真视频教程

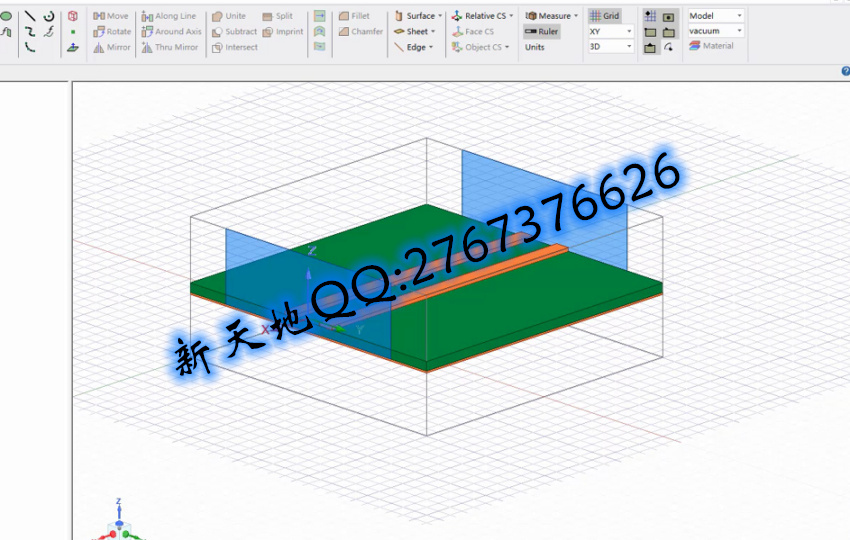

├┈T01_第一个HFSS仿真工程

├┈T02_仿真数据后处理

├┈T03_参数化建模

├┈T04_梯形横截面信号线及表面绿油建模

├┈T05_AC耦合电容焊盘仿真建模

├┈T06_AC耦合电容焊盘阻抗优化仿真_TDR仿真

├┈T07_差分孔仿真优化_叠层建模

├┈T08_差分孔仿真优化_过孔建模2

├┈T09_差分孔仿真优化_过孔建模3

├┈T10_差分孔仿真优化_仿真设置

├┈T11_差分孔仿真优化_共用反焊盘优化

├┈T12_差分孔自动化建模_ViaWizard

├┈T13_同轴线引入和差分线引入的TDR对比

├┈T14_类BGA扇出孔建模仿真

├┈T15_BGA扇出不同处理方式下TDR差异

├┈T16_BGA焊盘挖空_使用Lumport仿真

├┈T17_IC_PAD_阻抗优化仿真

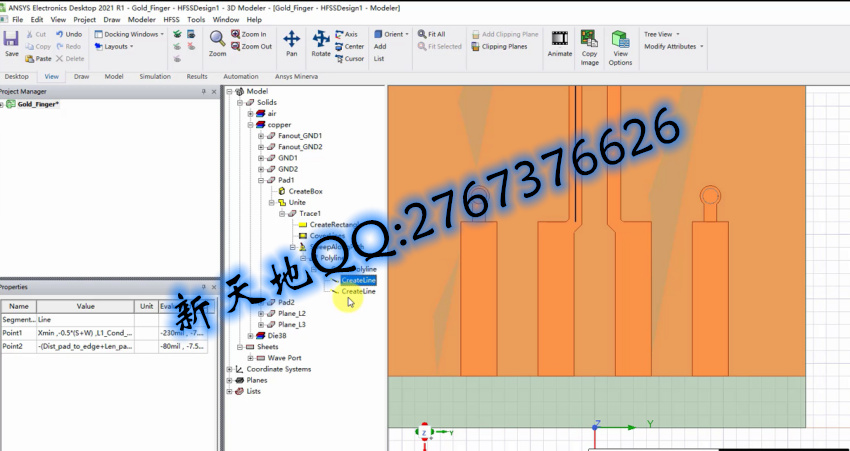

├┈T18_金手指仿真建模说明

├┈T19_金手指仿真_如何设置端口更合理

├┈T20_切割PCB

├┈T21_切割结构导入HFSS

├┈T22_模型处理_激励-边界条件_仿真设置_

├┈T23_差分对的频变阻抗_查看网格划分

├┈T24_DeltaS_DeltaZ0_对仿真结果的影响

├┈T25_差分线长度不同情况下求解结果差异的原因

├┈T26_提高仿真精度后的结果_端口去嵌

├┈T27_其他常用号仿真选项的含义

├┈T28_Waveport与Lumpedport的用法

◆02.信号完整性SI基础教程

├┈1.1-SI开营分享

├┈2.1-Base_任务01_上升时间与频谱分量的关系

├┈3.1-Base_任务02_上升时间与带宽的关系

├┈4.1-Base_任务03_信号的动态传播

├┈5.1-Base_任务04_导体结构的互容C互感L

├┈6.1-Base_任务05_返回路径上的电流

├┈7.1-Base_任务06_返回电流的二维分布1

├┈8.1-Base_任务07_返回电流的二维分布2

├┈9.1-Base_任务08_单位长度电感L单位长度电容C

├┈10.1-Base_任务09_信号传播速度与延时

├┈11.1-Base_任务10_信号看到的阻抗及传输线特性阻抗

├┈12.1-Base_任务11_参考平面与返回电流_part1

├┈13.1-Base_任务11_参考平面与返回电流_part2

├┈14.1-Base_任务12_损耗及其对信号的影响

├┈15.1-RefL_任务01_反射规律

├┈16.1-RefL_任务02_多次反射与振铃

├┈17.1-RefL_任务03_反射波的形状

├┈18.1-RefL_任务04_下降沿处的振铃

├┈19.1-RefL_任务05_Tr不为0的信号反射情况

├┈20.1-RefL_任务06_电容的反射特性

├┈21.1-RefL_任务07_电感的反射特性

├┈22.1-RefL_任务08_过冲_临界长度_端接

├┈23.1-RefL_任务09_串联端接

├┈24.1-RefL_任务10_串接端接stub影响及波形解读

├┈25.1-RefL_任务11_末端并接端接

├┈26.1-RefL_任务12_Die电容引起的反射

├┈27.1-RefL_任务13_分支结构中的反射

├┈28.1-RefL_任务14_T拓扑结构的特性_part1

├┈29.1-RefL_任务14_T拓扑结构的特性_part2

├┈30.1-RefL_任务15_链式结构的特性

├┈31.1-RefL_任务16_FLY-BY结构中容性负载的影响

├┈32.1-XTK_任务01_容性耦合与容性串扰噪声

├┈33.1-XTK_任务02_感性耦合与感性串扰噪声

├┈34.1-XTK_任务03_仿真近端串扰远端串扰

├┈35.1-XTK_任务04_近端串扰的饱和

├┈36.1-XTK_任务05_远端串扰的饱和

├┈37.1-XTK_任务06_远端串扰表层内层

├┈38.1-XTK_任务07_近端串扰有多大

├┈39.1-XTK_任务08_多条攻击线时的近端串扰

├┈40.1-XTK_任务09_影响串扰的因素

├┈41.1-XTK_任务10_介质厚度与串扰

├┈42.1-XTK_任务11_Er_Hsub与串扰

├┈43.1-XTK_任务12_宽边耦合的串扰

├┈44.1-XTK_任务13_串扰对信号的影响

├┈45.1-XTK_任务14_串扰如何影响信号边沿

├┈46.1-XTK_任务15_蛇形绕线中的延时

├┈47.1-XTK_任务16_反射串扰的纠缠

├┈48.1-自测任务

├┈49.1-自测任务演示1

├┈49.2-自测任务演示2

├┈49.3-自测任务演示3

├┈50.1-综合01_综合任务及思路导引

├┈50.2-综合02_写操作仿真

├┈50.3-综合03_读操作仿真

├┈50.4-综合04_解决规避风险问题

├┈50.5-综合完结_FLASH接口仿真过程记录

◆03.电源完整性PI教程

├┈1_开始前必看-如何高效训练

├┈2_T01_麻烦的根源_数字IC的动态电流

├┈3_T02_动态电流怎样产生电源噪声的

├┈4_T03_解惑纷乱的VRM模型

├┈5_T04_目标阻抗设计方法

├┈6_T05_仿真观察电容的特性

├┈7_T06_电容并联是怎样压低阻抗的

├┈8_T07_仿真观察并联谐振峰的特性

├┈9_T08_怎样确定电容网络中的大电容

├┈10_T09_电容网络配置方法

├┈11_T10_该在多大频率范围内去耦

├┈12_T11_电感_PDN中最重要的参数

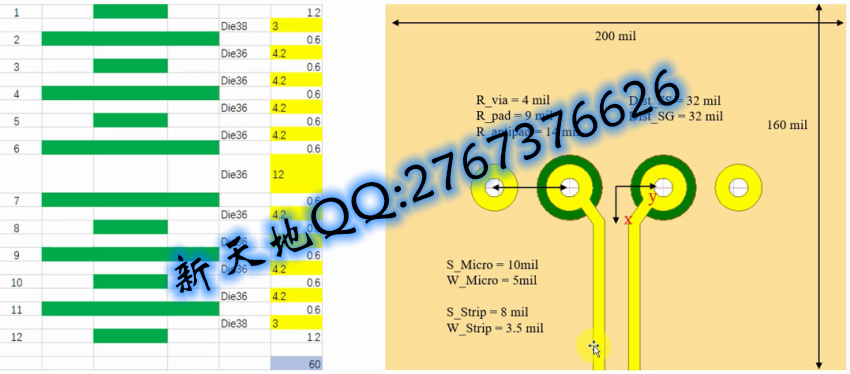

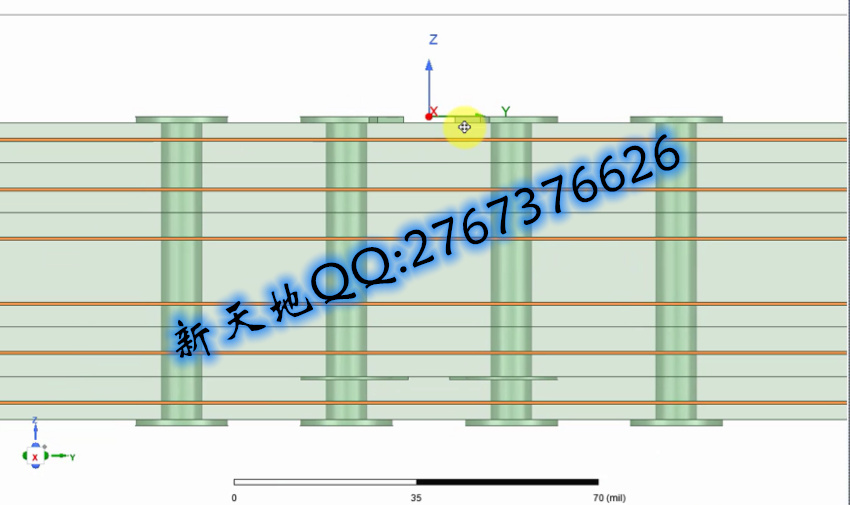

├┈13_T12_电容扇出孔叠层参数化建模

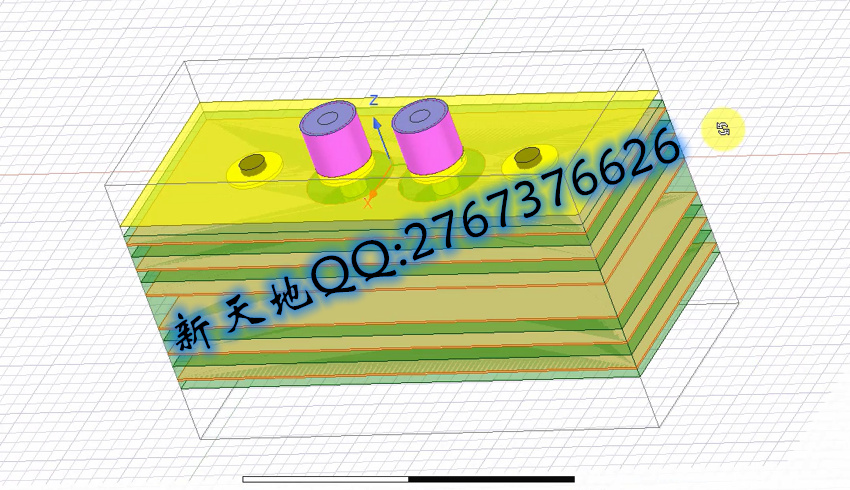

├┈14_T13_电容扇出过孔建模_布尔运算

├┈15_T14_电容焊盘及扇出线建模

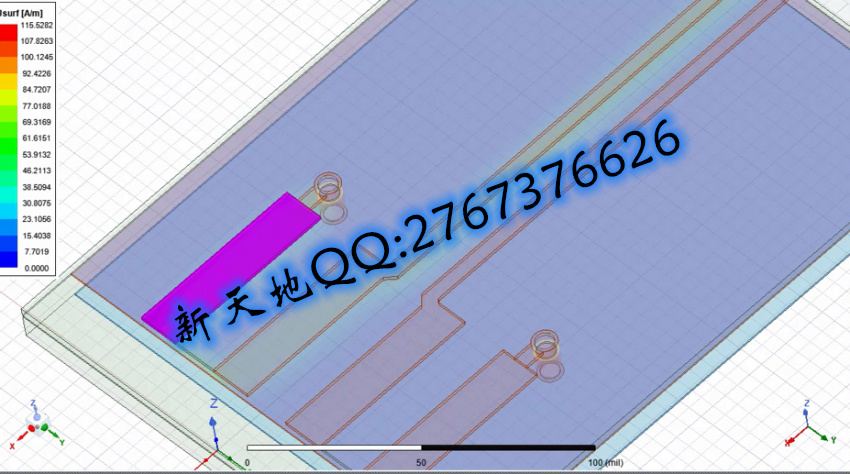

├┈16_T15_怎样仿真电容的安装电感

├┈17_T16_是什么影响了电容安装电感

├┈18_T17_仿真观察平面电感

├┈19_T18_仿真观察孔洞对平面电感的影响

├┈20_T19_电容位置的影响_另一种评估方法

├┈21_T20_仿真观察补偿电流与电压波动

├┈22_T21_仿真PDN频域阻抗

├┈23_T22_Mask_模型文件_Port复用

├┈24_T23_解决不满足Spec问题_1

├┈25_T24_解决不满足Spec问题_2

├┈26_T25_解决不满足Spec问题_3

├┈27_T26_Open_Short_Impedance

├┈28_T27_数字IC电源供电路径上的磁珠滤波

├┈29_T28_PowerDC仿真IRDrop和DCR

├┈30_T29_怎样用PowerSI精确仿真DCR值

├┈31_A1 为什么端口阻抗不用50欧姆

├┈32_A2 如何利用PDN阻抗计算电感量

├┈33_A3 为什么有时候加的电容似乎不起作用

◆04.SIPI项目分析教程

├┈001.T00_项目训练介绍及第1个任务

├┈002.T01_PDN阻抗仿真避坑(1)

├┈003.T02_PDN阻抗仿真避坑(2)

├┈004.T03_PDN阻抗仿真避坑(3)

├┈005.T04_Short Circuit Impedance 仿真

├┈006.T05_PDN阻抗仿真操作全过程记录

├┈007.T06_VDD_MPU_DCR仿真

├┈008.T07_DDR接口PDN阻抗仿真

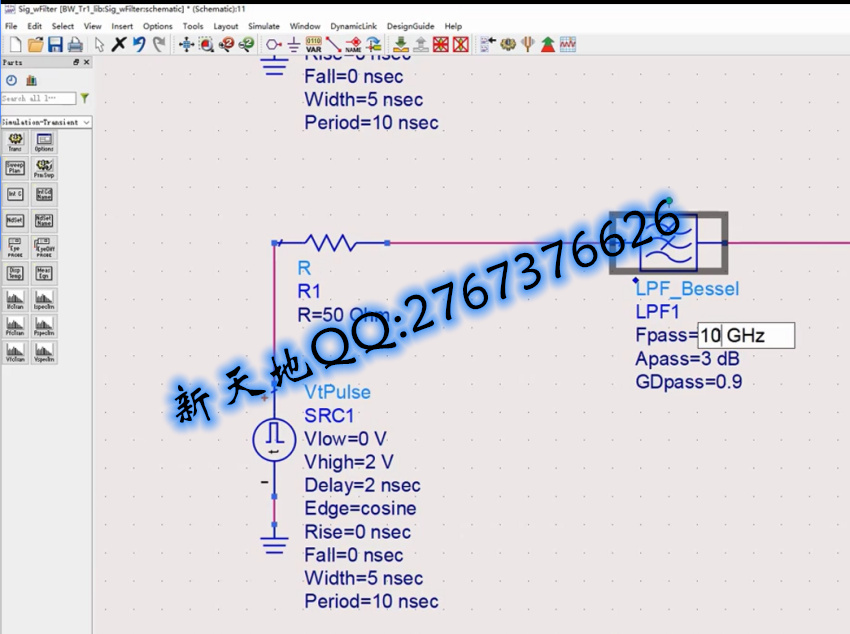

├┈009.T08_IBIS模型

├┈010.T09_QSPI_FLASH_01

├┈011.T10_QSPI_FLASH_02_如何判断信号质量是否满足要求

├┈012.T11_QSPI_FLASH_03_信号优化及时序参数

├┈013.T12_EMMC接口仿真

├┈014.T13_DDR接口仿真01

├┈015.T14_DDR接口仿真02

├┈016.T15_DDR接口信号质量

├┈017.T16_时序参数及写操作时序余量分析

├┈018.T17_读操作及时序余量分析

├┈019.T18_Ethernet_100Base

├┈020.T19_Gbit_Ethernet

├┈021.T20_USB_关注哪些东西

├┈022.T21_USB_1_处理三维结构

├┈023.T21_USB_2_添加波端口矩形

├┈024.T21_USB_3_添加同轴端口

├┈025.T21_USB_4_添加空气盒子_激励

├┈026.T22_仿真设置及TDR

├┈027.T23_连接器Pindrill建模优化反焊盘

├┈028.T24_差分孔建模优化

├┈029.T25_大焊盘参考面挖空建模优化

├┈030.T26_PCIE接口仿真优化

├┈031.T27_HDMI接口仿真

├┈032.T28_Profibus_CAN_RS485

◆05.S参数及耦合干扰分析教程

├┈1_S01_Z参数的含义

├┈2_S02_输入阻抗Zin与反射系数

├┈3_S03_S参数的含义

├┈4_S04_计算一个二端口网络的S参数

├┈5_S05_S参数形式及曲线特征

├┈6_S06_S参数中的纹波

├┈7_S07_S参数与Z参数的关系

├┈8_S08_S11与传输线阻抗

├┈9_S09_S21与相位延迟

├┈10_S10_耦合线4端口S参数及其特征

├┈11_S11_典型结构的S参数特征

├┈12_S12_MixedMode01_与单端S参数的关系

├┈13_S12_MixedMode02_深度解读差分参数

├┈14_S12_MixedMode03_深度解读模态转换

├┈15_S13_Passivity Causality Stability

├┈16_S14_TDR_TDT

├┈17_S15_TDR_多次反射引起的读取误差

├┈18_S16_上升时间对TDR阻抗的影响

├┈19_S17_TDR分辨率问题

├┈20_S18_损耗对于TDR曲线的影响

├┈21_S19_参考阻抗对TDR阻抗曲线的影响

├┈22_S20_S参数带宽对TDR曲线的影响

├┈23_S21_差分TDR仿真

├┈24_S22_TDR TDT与S参数的关系

├┈25_N01_孔与线之间的耦合干扰

├┈26_N02_连接器PIN定义与耦合干扰

├┈27_N03_平面缺失导致的层间耦合

├┈28_N04_层间耦合对信号的影响

├┈29_N05_边缘场导致的层间耦合

├┈30_N06_跨分割_仿真方法校准

├┈31_N07_跨分割_如何处理边界条件

├┈32_N08_跨分割_内层走线如何设置Port

├┈33_N09_跨分割_Waveport or Lumport

├┈34_N10_跨分割_评估对耦合干扰的影响

├┈35_N11_跨SLOT引起的耦合干扰

├┈36_N12_Slot附近的信号线受干扰情况

├┈37_N13_临近完整平面的作用

├┈38_N14_板间互连地线导致的问题

├┈39_N14_回流路径上的电容与谐振

├┈40_N15_参考无关平面时的串扰恶化_01

├┈41_N15_参考无关平面时的串扰恶化_02

├┈42_N16_大尺寸PCB内部的孔间串扰

├┈43_N17_Coupled_Stub 的影响

├┈44_N18_BGA下过孔密集区域的孔间串扰

├┈45_N19_PowerVia对串扰的影响

├┈46_N20_腔体谐振与边界条件

├┈47_N21_腔体谐振对孔间串扰的影响

├┈48_N22_过孔密集区域的孔间串扰与腔体谐振

├┈49_N23_电源平面对信号线的耦合干扰

├┈50_N24_信号线对电源平面的耦合干扰

├┈51_N25_共用电源平面的负载间耦合干扰

├┈52_N26_电源平面之间的耦合干扰

◆06.DDR SIPI分析教程

├┈1_T00 训练营介绍

├┈2_T01_接口信号电源梳理SSTL逻辑及特性

├┈3_T02_信号质量要求_Ron_Z0_ODT对眼图影响

├┈4_T03_怎样优化DQ信号质量

├┈5_T04_如何预判眼图风险

├┈6_T05_哪些因素会影响时序余量

├┈7_T06_地址信号树型结构的脾气

├┈8_T07_阻抗突变及串扰的影响

├┈9_T08_PDN验证及优化

├┈10_T09_VREF控制要点及优化方向

├┈11_T10_DDR3接口SIPI设计优化要点总结

├┈12_T11_DDR4的变化_了解POD的脾气

├┈13_T12_BER眼图模板_BER意义下的眼图睁开程度

├┈14_T13_ISI_XTK对眼图的影响

├┈15_T14_SSN对眼图的影响

├┈16_T15_眼图质量判断及风险控制

├┈17_T16_Read眼图_Package的影响

├┈18_T17_Read眼图_PDN优化改善眼图

├┈19_T18_AddCmd信号评估标准_FlyBy结构

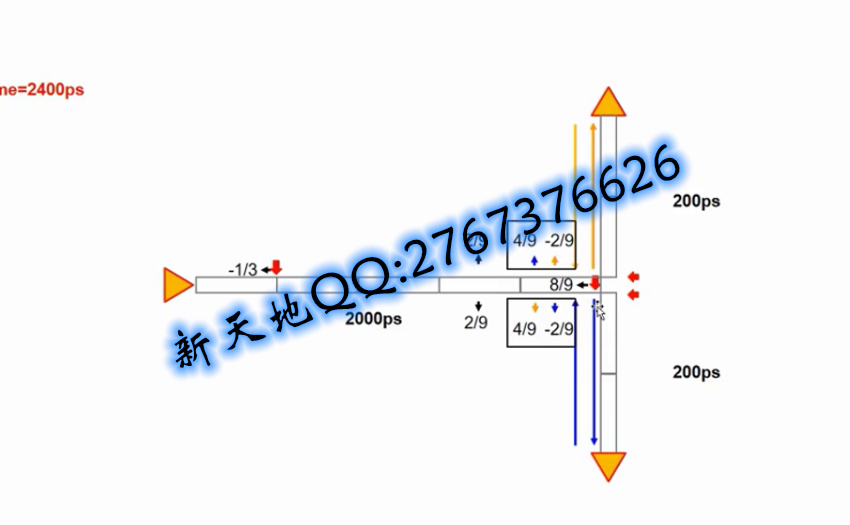

├┈20_T19_FlyBy结构_负载的反射

├┈21_T20_FlyBy结构_驱动器的反射

├┈22_T21_FlyBy结构_Rterm反射

├┈23_T22_周期性负载的反射与容性补偿

├┈24_T23_Fanout负载效应_Rterm优化

├┈25_T24_Pkg的影响

├┈26_T25_FlyBy结构_分段长度的影响

├┈27_T26_FlyBy结构_XTK_ISI

├┈28_T27_FlyBy结构_VTT电源的影响

├┈29_T28_DDR4接口SIPI设计优化要点总结

├┈30_T29_LPDDR4 PDN阻抗仿真及问题

├┈31_T30_LPDDR4 PDN阻抗优化措施参考

├┈32_T31_LPDDR4接口信号仿真小结

◆07.高速差分分析教程

├┈1_01_正确认识差分线

├┈2_02_临近导体对单端阻抗的影响

├┈3_03_差分阻抗

├┈4_04_紧耦合抗干扰能力真的强吗

├┈5_05_紧耦合引起的其他问题

├┈6_06_差分共模信号传输反射端接

├┈7_07_回流路径及耦合干扰问题

├┈8_08_Gbps高速差分系统设计要点综述

├┈9_09_损耗对眼图的影响辨析

├┈10_10_损耗引起的ISI问题

├┈11_11_ISI_Jitter_Mag

├┈12_12_均衡原理及CTLE

├┈13_13_FFE均衡原理

├┈14_14_DFE均衡原理

├┈15_15_频变介质特性及介质损耗

├┈16_16_趋肤效应导体损耗及表面粗糙度

├┈17_17_Stub产生的谐振

├┈18_18_Stub与阻抗不连续

├┈19_19_差分孔_非功能焊盘_残桩

├┈20_20_差分孔_孔距_反焊盘尺寸

├┈21_21_差分孔_孔径_GND孔数量

├┈22_22_差分孔_反焊盘形状

├┈23_23_差分孔_线孔转换部分的影响

├┈24_24_差分孔_反焊盘tap及综合阻抗优化

├┈25_25_差分孔_临近的电源孔的影响_思路分析

├┈26_26_差分孔_临近的电源孔对无源结构特性的影响

├┈27_27_差分孔_信号对模拟电源的噪声耦合

├┈28_28_差分孔_数字电源对信号孔的噪声耦合

├┈29_29_AC耦合电容_阻抗优化

├┈30_30_电容三维结构的影响

├┈31_31_电容三维结构与S参数中的谐振

├┈32_32_电容参考面挖空与噪声耦合

├┈33_33_模态转换的根源

├┈34_34_从S参数视角理解什么是不对称

├┈35_35_Skew对S参数的影响

├┈36_36_Skew的来源

├┈37_37_阻抗突变点数量及间距对模态转换的影响

├┈38_38_差分孔位置处的模态转换

├┈39_39_表层差分线BGA处回流不顺引起的问题

├┈40_40_内层差分线BGA处回流不顺引起的问题1

├┈41_41_内层差分线BGA处回流不顺引起的问题2

├┈42_42_内层差分线BGA处回流不顺引起的问题3

├┈43_43_金手指位置回流引入的Stub

├┈44_44_考虑连接器两侧情况下的分析

├┈45_45_多个阻抗不连续点的影响

├┈46_46_电源时钟及耦合干扰

◆08.信号完整性高级分析视频

├┈01_《信号完整性揭秘》视频(第1集)方波信号的频谱特征

├┈02_《信号完整性揭秘》视频(第2集)信号上升时间与带宽

├┈03_《信号完整性揭秘》视频(第3集)传输线行为特征及信号传播

├┈04_《信号完整性揭秘》视频(第4集)传输线电容

├┈05_《信号完整性揭秘》视频(第5集)传输线电感

├┈06_《信号完整性揭秘》视频(第6集)瞬时阻抗和特性阻抗

├┈07_《信号完整性揭秘》视频(第7集)影响特性阻抗的因素

├┈08_《信号完整性揭秘》视频(第8集)参考平面和返回电流

├┈09_《信号完整性揭秘》视频(第9集)传输线延时与模型

├┈10_《信号完整性揭秘》视频(第10集)耦合传输线

├┈11_《信号完整性揭秘》视频(第11集)有损传输线

├┈12_《信号完整性揭秘》视频(第12集)介质损耗

├┈13_《信号完整性揭秘》视频(第13集)信号的反射

├┈14_《信号完整性揭秘》视频(第14集)信号振铃

├┈15_《信号完整性揭秘》视频(第15集)正反射负反射

├┈16_《信号完整性揭秘》视频(第16集)上升时间与反射

├┈17_《信号完整性揭秘》视频(第17集)容性阻抗不连续

├┈18_《信号完整性揭秘》视频(第18集)末端电容的反射

├┈19_《信号完整性揭秘》视频(第19集)线路中电容反射

├┈20_《信号完整性揭秘》视频(第20集)电容引起的时间延迟

├┈21_《信号完整性揭秘》视频(第21集)周期性容性负载

├┈22_《信号完整性揭秘》视频(第22集)Stub的影响

├┈23_《信号完整性揭秘》视频(第23集)临界长度

├┈24_《信号完整性揭秘》视频(第24集)线长与端接

├┈25_《信号完整性揭秘》视频(第25集)Driver的输出阻抗

├┈26_《信号完整性揭秘》视频(第26集)端接方法

├┈27_《信号完整性揭秘》视频(第27集)拓扑结构

├┈28_《信号完整性揭秘》视频(第28集)端接中的桩线

├┈29_《信号完整性揭秘》视频(第29集)阻尼电阻

├┈30_《信号完整性揭秘》视频(第30集)串扰根源

├┈31_《信号完整性揭秘》视频(第31集)容性感性串扰

├┈32_《信号完整性揭秘》视频(第32集)近端串扰远端串扰

├┈33_《信号完整性揭秘》视频(第33集)近端串扰的饱和

├┈34_《信号完整性揭秘》视频(第34集)远端串扰的饱和

├┈35_《信号完整性揭秘》视频(第35集)边沿耦合宽边耦合

├┈36_《信号完整性揭秘》视频(第36集)影响串扰的因素

├┈37_《信号完整性揭秘》视频(第37集)串扰对信号的影响

├┈38_《信号完整性揭秘》视频(第38集)蛇形走线与延迟

├┈39_《信号完整性揭秘》视频(第39集)保护地线

├┈40_《信号完整性揭秘》视频(第40集)差分传输

├┈41_《信号完整性揭秘》视频(第41集)差分返回电流

├┈42_《信号完整性揭秘》视频(第42集)差分对阻抗参数

├┈43_《信号完整性揭秘》视频(第43集)差分对端接

├┈44_《信号完整性揭秘》视频(第44集)差分对串扰

├┈45_《信号完整性揭秘》视频(第45集)模态转换

├┈46_《信号完整性揭秘》视频(第46集)等长等距

├┈47_《信号完整性揭秘》视频(第47集)松耦合还是紧耦合

├┈48_《信号完整性揭秘》视频(第48集)PDN系统噪声来源

├┈49_《信号完整性揭秘》视频(第49集)电容去耦的两种解释

├┈50_《信号完整性揭秘》视频(第50集)实际电容特性

├┈51_《信号完整性揭秘》视频(第51集)目标阻抗设计方法

├┈52_《信号完整性揭秘》视频(第52集)并联电容及谐振峰

├┈53_《信号完整性揭秘》视频(第53集)去耦电容配置方法

◆SIwave电源完整性仿真资料PDF

大小26.37G字节.